Resumo da pastilha de SiC

wafers de carbeto de silício (SiC)Os substratos de silício se tornaram a escolha preferencial para eletrônica de alta potência, alta frequência e alta temperatura nos setores automotivo, de energia renovável e aeroespacial. Nosso portfólio abrange politipos e esquemas de dopagem essenciais — 4H dopado com nitrogênio (4H-N), semi-isolante de alta pureza (HPSI), 3C dopado com nitrogênio (3C-N) e 4H/6H tipo p (4H/6H-P) — oferecidos em três níveis de qualidade: PRIME (substratos totalmente polidos, de grau de dispositivo), DUMMY (lapidados ou não polidos para testes de processo) e RESEARCH (camadas epitaxiais e perfis de dopagem personalizados para P&D). Os diâmetros dos wafers variam de 2″, 4″, 6″, 8″ e 12″ para atender tanto equipamentos legados quanto fábricas avançadas. Também fornecemos lingotes monocristalinos e cristais-semente precisamente orientados para dar suporte ao crescimento de cristais em nossas instalações.

Nossos wafers 4H-N apresentam densidades de portadores de 1×10¹⁶ a 1×10¹⁹ cm⁻³ e resistividades de 0,01–10 Ω·cm, proporcionando excelente mobilidade eletrônica e campos de ruptura acima de 2 MV/cm — ideais para diodos Schottky, MOSFETs e JFETs. Os substratos HPSI excedem a resistividade de 1×10¹² Ω·cm com densidades de microporos abaixo de 0,1 cm⁻², garantindo vazamento mínimo para dispositivos de RF e micro-ondas. O 3C-N cúbico, disponível nos formatos de 2″ e 4″, permite heteroepitaxia em silício e suporta novas aplicações fotônicas e MEMS. Wafers 4H/6H-P do tipo P, dopados com alumínio em concentrações de 1×10¹⁶ a 5×10¹⁸ cm⁻³, facilitam arquiteturas de dispositivos complementares.

As pastilhas de SiC, PRIME, passam por polimento químico-mecânico para rugosidade superficial RMS <0,2 nm, variação de espessura total inferior a 3 µm e curvatura <10 µm. Os substratos DUMMY aceleram os testes de montagem e encapsulamento, enquanto as pastilhas RESEARCH apresentam espessuras de camada epitaxial de 2 a 30 µm e dopagem personalizada. Todos os produtos são certificados por difração de raios X (curva de oscilação <30 segundos de arco) e espectroscopia Raman, com testes elétricos — medições de efeito Hall, perfil C-V e varredura de micropipe — garantindo a conformidade com as normas JEDEC e SEMI.

Boules de até 150 mm de diâmetro são cultivados via PVT e CVD com densidades de deslocamento abaixo de 1×10³ cm⁻² e baixa contagem de microporos. Os cristais-semente são cortados com uma precisão de 0,1° em relação ao eixo c para garantir crescimento reprodutível e alto rendimento de fatiamento.

Ao combinar múltiplos politipos, variantes de dopagem, níveis de qualidade, tamanhos de wafers de SiC e produção interna de lingotes e cristais-semente, nossa plataforma de substrato de SiC otimiza as cadeias de suprimentos e acelera o desenvolvimento de dispositivos para veículos elétricos, redes inteligentes e aplicações em ambientes extremos.

Resumo da pastilha de SiC

wafers de carbeto de silício (SiC)O silício (SiC) tornou-se o substrato de escolha para eletrônica de alta potência, alta frequência e alta temperatura nos setores automotivo, de energia renovável e aeroespacial. Nosso portfólio abrange os principais politipos e esquemas de dopagem — 4H dopado com nitrogênio (4H-N), semi-isolante de alta pureza (HPSI), 3C dopado com nitrogênio (3C-N) e 4H/6H tipo p (4H/6H-P) — oferecidos em três graus de qualidade: wafer de SiCPRIME (substratos totalmente polidos, de qualidade para dispositivos), DUMMY (lapidados ou não polidos para testes de processo) e RESEARCH (camadas epitaxiais personalizadas e perfis de dopagem para P&D). Os diâmetros dos wafers de SiC variam de 2", 4", 6", 8" e 12" para atender tanto equipamentos tradicionais quanto fábricas de última geração. Também fornecemos lingotes monocristalinos e cristais-semente precisamente orientados para dar suporte ao crescimento de cristais em nossas instalações.

Nossos wafers de SiC 4H-N apresentam densidades de portadores de 1×10¹⁶ a 1×10¹⁹ cm⁻³ e resistividades de 0,01–10 Ω·cm, proporcionando excelente mobilidade eletrônica e campos de ruptura acima de 2 MV/cm — ideais para diodos Schottky, MOSFETs e JFETs. Os substratos HPSI excedem a resistividade de 1×10¹² Ω·cm com densidades de microporos abaixo de 0,1 cm⁻², garantindo vazamento mínimo para dispositivos de RF e micro-ondas. O SiC cúbico 3C-N, disponível nos formatos de 2″ e 4″, permite heteroepitaxia em silício e suporta novas aplicações fotônicas e MEMS. Os wafers de SiC tipo P 4H/6H-P, dopados com alumínio a uma concentração de 1×10¹⁶–5×10¹⁸ cm⁻³, facilitam arquiteturas de dispositivos complementares.

As lâminas de SiC PRIME passam por polimento químico-mecânico para rugosidade superficial RMS <0,2 nm, variação de espessura total inferior a 3 µm e curvatura <10 µm. Os substratos DUMMY aceleram os testes de montagem e encapsulamento, enquanto as lâminas RESEARCH apresentam espessuras de camada epitaxial de 2 a 30 µm e dopagem personalizada. Todos os produtos são certificados por difração de raios X (curva de oscilação <30 segundos de arco) e espectroscopia Raman, com testes elétricos — medições de efeito Hall, perfil C-V e varredura de micropipe — garantindo a conformidade com as normas JEDEC e SEMI.

Boules de até 150 mm de diâmetro são cultivados via PVT e CVD com densidades de deslocamento abaixo de 1×10³ cm⁻² e baixa contagem de microporos. Os cristais-semente são cortados com uma precisão de 0,1° em relação ao eixo c para garantir crescimento reprodutível e alto rendimento de fatiamento.

Ao combinar múltiplos politipos, variantes de dopagem, níveis de qualidade, tamanhos de wafers de SiC e produção interna de lingotes e cristais-semente, nossa plataforma de substrato de SiC otimiza as cadeias de suprimentos e acelera o desenvolvimento de dispositivos para veículos elétricos, redes inteligentes e aplicações em ambientes hostis.

Folha de dados do wafer de SiC tipo 4H-N de 6 polegadas

| Folha de dados de wafers de SiC de 6 polegadas | ||||

| Parâmetro | Subparâmetro | Grau Z | Grau P | Nota D |

| Diâmetro | 149,5–150,0 mm | 149,5–150,0 mm | 149,5–150,0 mm | |

| Grossura | 4H‑N | 350 µm ± 15 µm | 350 µm ± 25 µm | 350 µm ± 25 µm |

| Grossura | 4H‑SI | 500 µm ± 15 µm | 500 µm ± 25 µm | 500 µm ± 25 µm |

| Orientação do wafer | Fora do eixo: 4,0° em direção a <11-20> ±0,5° (4H-N); No eixo: <0001> ±0,5° (4H-SI) | Fora do eixo: 4,0° em direção a <11-20> ±0,5° (4H-N); No eixo: <0001> ±0,5° (4H-SI) | Fora do eixo: 4,0° em direção a <11-20> ±0,5° (4H-N); No eixo: <0001> ±0,5° (4H-SI) | |

| Densidade de microtubos | 4H‑N | ≤ 0,2 cm⁻² | ≤ 2 cm⁻² | ≤ 15 cm⁻² |

| Densidade de microtubos | 4H‑SI | ≤ 1 cm⁻² | ≤ 5 cm⁻² | ≤ 15 cm⁻² |

| Resistividade | 4H‑N | 0,015–0,024 Ω·cm | 0,015–0,028 Ω·cm | 0,015–0,028 Ω·cm |

| Resistividade | 4H‑SI | ≥ 1×10¹⁰ Ω·cm | ≥ 1×10⁵ Ω·cm | |

| Orientação plana primária | [10-10] ± 5,0° | [10-10] ± 5,0° | [10-10] ± 5,0° | |

| Comprimento plano primário | 4H‑N | 47,5 mm ± 2,0 mm | ||

| Comprimento plano primário | 4H‑SI | Entalhe | ||

| Exclusão de borda | 3 mm | |||

| Warp/LTV/TTV/Arco | ≤2,5 µm / ≤6 µm / ≤25 µm / ≤35 µm | ≤5 µm / ≤15 µm / ≤40 µm / ≤60 µm | ||

| Rugosidade | polonês | Ra ≤ 1 nm | ||

| Rugosidade | CMP | Ra ≤ 0,2 nm | Ra ≤ 0,5 nm | |

| Rachaduras nas bordas | Nenhum | Comprimento cumulativo ≤ 20 mm, único ≤ 2 mm | ||

| Placas hexagonais | Área cumulativa ≤ 0,05% | Área cumulativa ≤ 0,1% | Área cumulativa ≤ 1% | |

| Áreas de politipagem | Nenhum | Área cumulativa ≤ 3% | Área cumulativa ≤ 3% | |

| Inclusões de carbono | Área cumulativa ≤ 0,05% | Área cumulativa ≤ 3% | ||

| Arranhões superficiais | Nenhum | Comprimento cumulativo ≤ 1 × diâmetro do wafer | ||

| Lascas de borda | Nenhuma permitida ≥ 0,2 mm de largura e profundidade | Até 7 lascas, ≤ 1 mm cada | ||

| TSD (Deslocamento da rosca do parafuso) | ≤ 500 cm⁻² | N / D | ||

| BPD (Deslocamento do Plano Base) | ≤ 1000 cm⁻² | N / D | ||

| Contaminação de superfície | Nenhum | |||

| Embalagem | Cassete multi-wafer ou recipiente para wafer único | Cassete multi-wafer ou recipiente para wafer único | Cassete multi-wafer ou recipiente para wafer único | |

Folha de dados do wafer de SiC tipo 4H-N de 4 polegadas

| Folha de dados do wafer de SiC de 4 polegadas | |||

| Parâmetro | Produção de MPD Zero | Grau de Produção Padrão (Grau P) | Nota fictícia (Nota D) |

| Diâmetro | 99,5 mm–100,0 mm | ||

| Espessura (4H-N) | 350 µm ± 15 µm | 350 µm ± 25 µm | |

| Espessura (4H-Si) | 500 µm ± 15 µm | 500 µm±25 µm | |

| Orientação do wafer | Fora do eixo: 4,0° em direção a <1120> ±0,5° para 4H-N; No eixo: <0001> ±0,5° para 4H-Si | ||

| Densidade de microtubos (4H-N) | ≤0,2 cm⁻² | ≤2 cm⁻² | ≤15 cm⁻² |

| Densidade de microtubos (4H-Si) | ≤1 cm⁻² | ≤5 cm⁻² | ≤15 cm⁻² |

| Resistividade (4H-N) | 0,015–0,024 Ω·cm | 0,015–0,028 Ω·cm | |

| Resistividade (4H-Si) | ≥1E10 Ω·cm | ≥1E5 Ω·cm | |

| Orientação plana primária | [10-10] ±5,0° | ||

| Comprimento plano primário | 32,5 mm ±2,0 mm | ||

| Comprimento plano secundário | 18,0 mm ±2,0 mm | ||

| Orientação plana secundária | Face de silício para cima: 90° no sentido horário a partir da superfície plana principal ±5,0° | ||

| Exclusão de borda | 3 mm | ||

| LTV/TTV/Deformação de Arco | ≤2,5 µm/≤5 µm/≤15 µm/≤30 µm | ≤10 µm/≤15 µm/≤25 µm/≤40 µm | |

| Rugosidade | Polimento Ra ≤1 nm; CMP Ra ≤0,2 nm | Ra ≤0,5 nm | |

| Rachaduras nas bordas causadas por luz de alta intensidade. | Nenhum | Nenhum | Comprimento cumulativo ≤10 mm; comprimento único ≤2 mm |

| Placas hexagonais por luz de alta intensidade | Área cumulativa ≤0,05% | Área cumulativa ≤0,05% | Área cumulativa ≤0,1% |

| Áreas politipadas por luz de alta intensidade | Nenhum | Área cumulativa ≤3% | |

| Inclusões Visuais de Carbono | Área cumulativa ≤0,05% | Área cumulativa ≤3% | |

| Arranhões na superfície de silício causados por luz de alta intensidade | Nenhum | Comprimento cumulativo ≤ 1 diâmetro de wafer | |

| Lascas nas bordas devido à luz de alta intensidade | Nenhuma largura ou profundidade permitida ≥0,2 mm | 5 permitidos, ≤1 mm cada | |

| Contaminação da superfície de silício por luz de alta intensidade | Nenhum | ||

| Deslocamento da rosca do parafuso | ≤500 cm⁻² | N / D | |

| Embalagem | Cassete multi-wafer ou recipiente para wafer único | Cassete multi-wafer ou recipiente para wafer único | Cassete multi-wafer ou recipiente para wafer único |

Folha de dados do wafer de SiC tipo HPSI de 4 polegadas

| Folha de dados do wafer de SiC tipo HPSI de 4 polegadas | |||

| Parâmetro | Grau de produção Zero MPD (Grau Z) | Grau de Produção Padrão (Grau P) | Nota fictícia (Nota D) |

| Diâmetro | 99,5–100,0 mm | ||

| Espessura (4H-Si) | 500 µm ±20 µm | 500 µm ±25 µm | |

| Orientação do wafer | Fora do eixo: 4,0° em direção a <11-20> ±0,5° para 4H-N; No eixo: <0001> ±0,5° para 4H-Si | ||

| Densidade de microtubos (4H-Si) | ≤1 cm⁻² | ≤5 cm⁻² | ≤15 cm⁻² |

| Resistividade (4H-Si) | ≥1E9 Ω·cm | ≥1E5 Ω·cm | |

| Orientação plana primária | (10-10) ±5,0° | ||

| Comprimento plano primário | 32,5 mm ±2,0 mm | ||

| Comprimento plano secundário | 18,0 mm ±2,0 mm | ||

| Orientação plana secundária | Face de silício para cima: 90° no sentido horário a partir da superfície plana principal ±5,0° | ||

| Exclusão de borda | 3 mm | ||

| LTV/TTV/Deformação de Arco | ≤3 µm/≤5 µm/≤15 µm/≤30 µm | ≤10 µm/≤15 µm/≤25 µm/≤40 µm | |

| Rugosidade (face C) | polonês | Ra ≤1 nm | |

| Rugosidade (face Si) | CMP | Ra ≤0,2 nm | Ra ≤0,5 nm |

| Rachaduras nas bordas causadas por luz de alta intensidade. | Nenhum | Comprimento cumulativo ≤10 mm; comprimento único ≤2 mm | |

| Placas hexagonais por luz de alta intensidade | Área cumulativa ≤0,05% | Área cumulativa ≤0,05% | Área cumulativa ≤0,1% |

| Áreas politipadas por luz de alta intensidade | Nenhum | Área cumulativa ≤3% | |

| Inclusões Visuais de Carbono | Área cumulativa ≤0,05% | Área cumulativa ≤3% | |

| Arranhões na superfície de silício causados por luz de alta intensidade | Nenhum | Comprimento cumulativo ≤ 1 diâmetro de wafer | |

| Lascas nas bordas devido à luz de alta intensidade | Nenhuma largura ou profundidade permitida ≥0,2 mm | 5 permitidos, ≤1 mm cada | |

| Contaminação da superfície de silício por luz de alta intensidade | Nenhum | Nenhum | |

| Deslocamento da rosca do parafuso | ≤500 cm⁻² | N / D | |

| Embalagem | Cassete multi-wafer ou recipiente para wafer único | ||

aplicação do wafer de SiC

-

Módulos de potência de wafer de SiC para inversores de veículos elétricos

MOSFETs e diodos baseados em wafers de SiC, construídos em substratos de wafers de SiC de alta qualidade, oferecem perdas de comutação ultrabaixas. Ao aproveitar a tecnologia de wafers de SiC, esses módulos de potência operam em tensões e temperaturas mais elevadas, possibilitando inversores de tração mais eficientes. A integração de chips de wafers de SiC nos estágios de potência reduz os requisitos de refrigeração e a área ocupada, demonstrando todo o potencial da inovação em wafers de SiC. -

Dispositivos de RF de alta frequência e 5G em wafer de SiC

Amplificadores e chaves de RF fabricados em plataformas de wafers de SiC semi-isolantes exibem condutividade térmica e tensão de ruptura superiores. O substrato de wafer de SiC minimiza as perdas dielétricas em frequências de GHz, enquanto a resistência do material permite uma operação estável sob condições de alta potência e alta temperatura, tornando o wafer de SiC o substrato ideal para estações base 5G e sistemas de radar de próxima geração. -

Substratos optoeletrônicos e de LED a partir de wafer de SiC

LEDs azuis e ultravioleta cultivados em substratos de silício (SiC) se beneficiam de excelente correspondência de rede cristalina e dissipação de calor. O uso de um substrato de SiC com face C polida garante camadas epitaxiais uniformes, enquanto a dureza inerente do SiC permite um afinamento preciso do substrato e uma embalagem confiável do dispositivo. Isso torna o substrato de SiC a plataforma ideal para aplicações de LEDs de alta potência e longa vida útil.

Perguntas e respostas sobre wafers de SiC

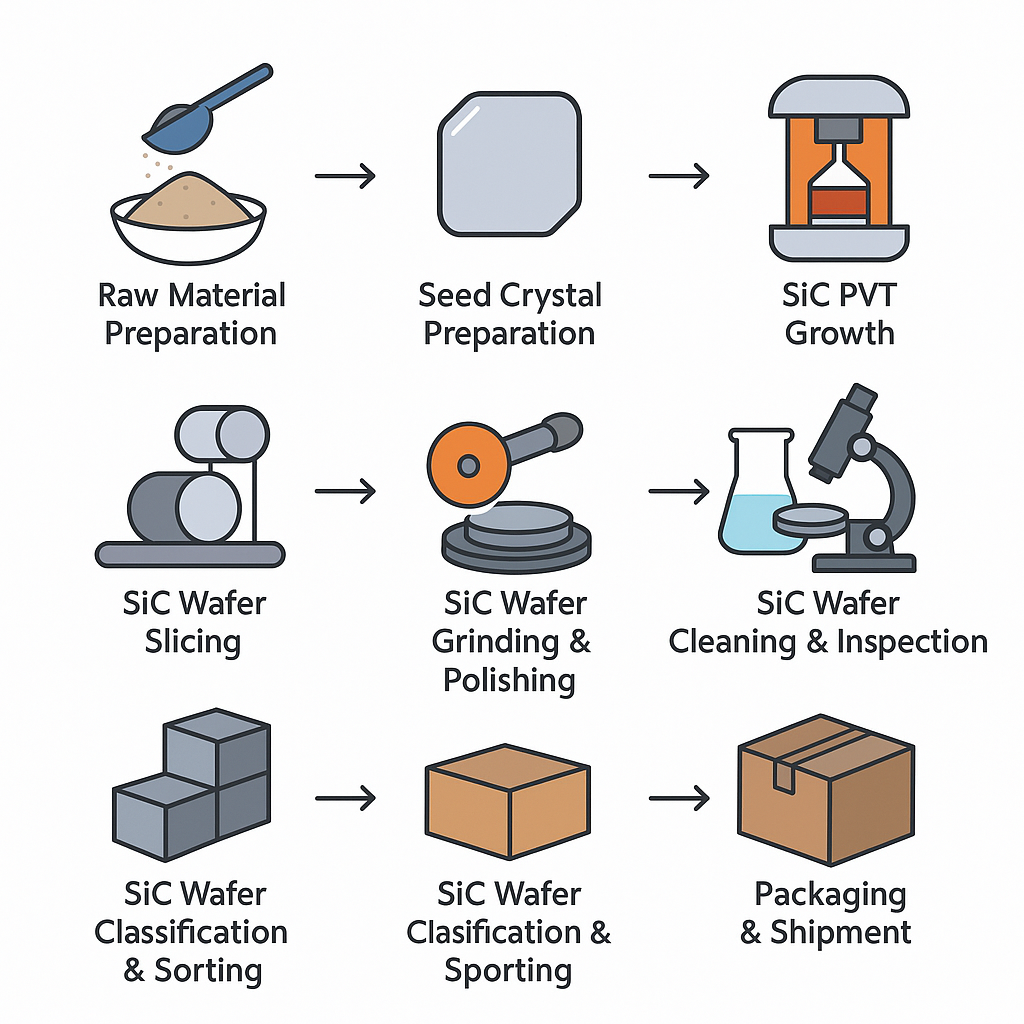

1. P: Como são fabricados os wafers de SiC?

UM:

wafers de SiC fabricadosPassos detalhados

-

wafers de SiCPreparação da matéria-prima

- Utilize pó de SiC com grau de pureza ≥5N (impurezas ≤1 ppm).

- Peneire e pré-asse para remover resíduos de carbono ou compostos de nitrogênio.

-

SiCPreparação de cristais-semente

-

Pegue um pedaço de monocristal de 4H-SiC e corte-o ao longo da orientação 〈0001〉 até obter uma área de aproximadamente 10 × 10 mm².

-

Polimento de precisão até Ra ≤0,1 nm e marcação da orientação do cristal.

-

-

SiCCrescimento PVT (Transporte Físico de Vapor)

-

Carregar o cadinho de grafite: fundo com pó de SiC, topo com cristal semente.

-

Evacue até 10⁻³–10⁻⁵ Torr ou preencha novamente com hélio de alta pureza a 1 atm.

-

A zona de fonte de calor deve estar a 2100–2300 ℃, enquanto a zona de sementes deve estar 100–150 ℃ mais fria.

-

Controle a taxa de crescimento entre 1 e 5 mm/h para equilibrar qualidade e produtividade.

-

-

SiCRecozimento de lingotes

-

Recozimento do lingote de SiC recém-crescido a 1600–1800 ℃ durante 4–8 horas.

-

Objetivo: aliviar as tensões térmicas e reduzir a densidade de deslocamentos.

-

-

SiCFatiamento de wafer

-

Utilize uma serra de fio diamantado para cortar o lingote em lâminas de 0,5 a 1 mm de espessura.

-

Minimize a vibração e a força lateral para evitar microfissuras.

-

-

SiCWaferRetificação e Polimento

-

Moagem grosseirapara remover danos causados pelo corte (rugosidade de aproximadamente 10–30 µm).

-

Moagem finapara obter uma planicidade ≤5 µm.

-

Polimento Químico-Mecânico (CMP)para alcançar um acabamento espelhado (Ra ≤0,2 nm).

-

-

SiCWaferLimpeza e Inspeção

-

Limpeza ultrassônicaem solução Piranha (H₂SO₄:H₂O₂), água DI e depois IPA.

-

Espectroscopia XRD/Ramanpara confirmar o politipo (4H, 6H, 3C).

-

Interferometriapara medir a planicidade (<5 µm) e a deformação (<20 µm).

-

Sonda de quatro pontospara testar a resistividade (ex: HPSI ≥10⁹ Ω·cm).

-

Inspeção de defeitossob microscópio de luz polarizada e testador de riscos.

-

-

SiCWaferClassificação e Ordenação

-

Classifique os wafers por politipo e tipo elétrico:

-

4H-SiC tipo N (4H-N): concentração de portadores 10¹⁶–10¹⁸ cm⁻³

-

4H-SiC Semi-Isolante de Alta Pureza (4H-HPSI): resistividade ≥10⁹ Ω·cm

-

6H-SiC tipo N (6H-N)

-

Outros: 3C-SiC, tipo P, etc.

-

-

-

SiCWaferEmbalagem e envio

2. P: Quais são as principais vantagens dos wafers de SiC em relação aos wafers de silício?

A: Em comparação com as lâminas de silício, as lâminas de SiC permitem:

-

Operação com tensão mais elevada(>1.200 V) com menor resistência em condução.

-

Maior estabilidade térmica(>300 °C) e melhor gestão térmica.

-

Velocidades de comutação mais rápidasCom menores perdas de comutação, reduzindo o resfriamento e o tamanho do sistema em conversores de potência.

4. P: Quais defeitos comuns afetam o rendimento e o desempenho dos wafers de SiC?

A: Os principais defeitos em wafers de SiC incluem microporos, deslocamentos no plano basal (BPDs) e arranhões superficiais. Microporos podem causar falhas catastróficas no dispositivo; BPDs aumentam a resistência no estado ligado ao longo do tempo; e arranhões superficiais levam à quebra do wafer ou ao crescimento epitaxial deficiente. Inspeções rigorosas e mitigação de defeitos são, portanto, essenciais para maximizar o rendimento dos wafers de SiC.

Data da publicação: 30 de junho de 2025