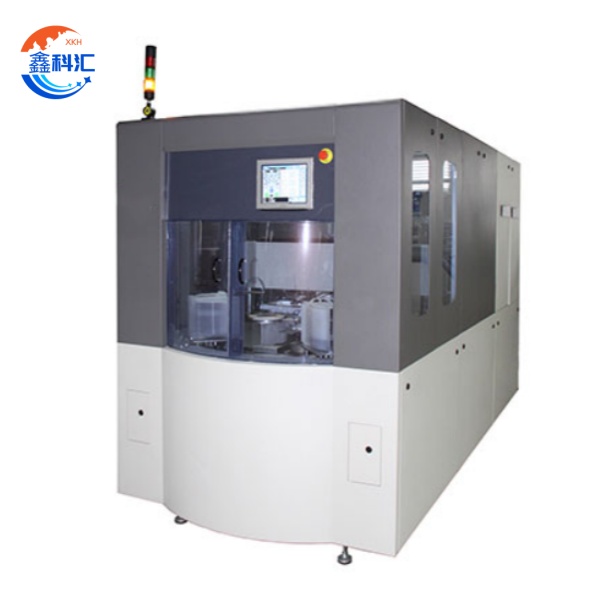

Equipamento para desbaste de wafers de safira/SiC/Si de 4 a 12 polegadas.

Princípio de funcionamento

O processo de adelgaçamento do wafer opera em três etapas:

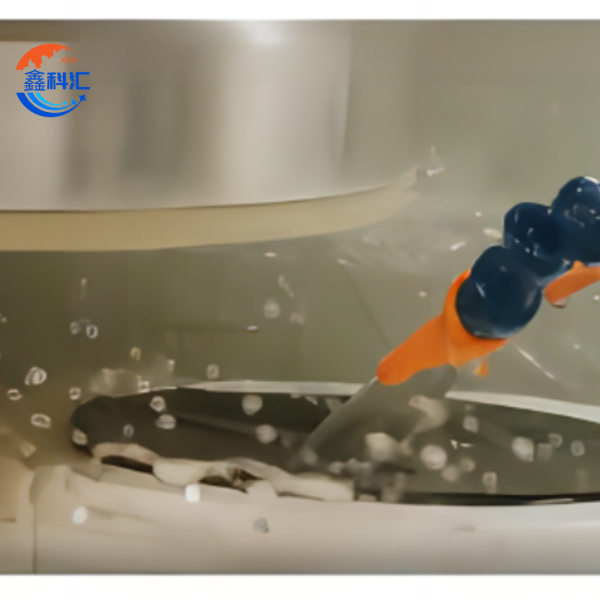

Desbaste: Uma rebolo diamantada (granulometria de 200 a 500 μm) remove de 50 a 150 μm de material a 3000 a 5000 rpm para reduzir rapidamente a espessura.

Retificação fina: Uma rebolo mais fina (granulometria de 1 a 50 μm) reduz a espessura para 20 a 50 μm a uma velocidade inferior a 1 μm/s para minimizar danos subsuperficiais.

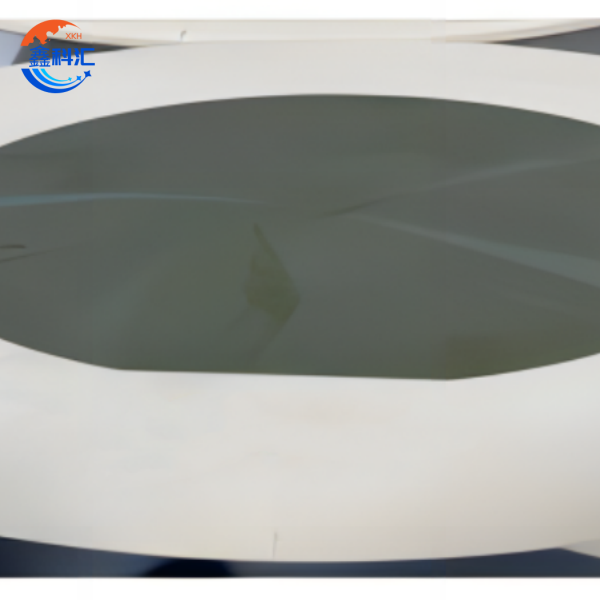

Polimento (CMP): Uma pasta químico-mecânica elimina danos residuais, atingindo Ra <0,1 nm.

Materiais Compatíveis

Silício (Si): Padrão para wafers CMOS, com espessura reduzida para 25 μm para empilhamento 3D.

Carboneto de silício (SiC): Requer rebolos diamantados especiais (concentração de diamante de 80%) para estabilidade térmica.

Safira (Al₂O₃): Refinada para 50 μm para aplicações em LEDs UV.

Componentes principais do sistema

1. Sistema de moagem

Retificadora de eixo duplo: Combina retificação grossa e fina em uma única plataforma, reduzindo o tempo de ciclo em 40%.

Eixo aerostático: faixa de velocidade de 0 a 6000 rpm com excentricidade radial <0,5 μm.

2. Sistema de Manuseio de Wafer

Placa de fixação a vácuo: força de retenção superior a 50 N com precisão de posicionamento de ±0,1 μm.

Braço robótico: Transporta wafers de 4 a 12 polegadas a 100 mm/s.

3. Sistema de Controle

Interferometria a laser: Monitoramento de espessura em tempo real (resolução de 0,01 μm).

Feedforward baseado em IA: prevê o desgaste das rodas e ajusta os parâmetros automaticamente.

4. Resfriamento e Limpeza

Limpeza ultrassônica: Remove partículas >0,5 μm com 99,9% de eficiência.

Água deionizada: Resfria o wafer a uma temperatura inferior a 5°C acima da temperatura ambiente.

Principais vantagens

1. Ultra-alta precisão: TTV (Variação total da espessura) <0,5 μm, WTW (Variação da espessura dentro do wafer) <1 μm.

2. Integração de múltiplos processos: Combina retificação, CMP e gravação a plasma em uma única máquina.

3. Compatibilidade de materiais:

Silício: Redução da espessura de 775 μm para 25 μm.

SiC: Atinge TTV <2 μm para aplicações de RF.

Wafers dopados: Wafers de InP dopados com fósforo com deriva de resistividade <5%.

4. Automação Inteligente: A integração do MES reduz o erro humano em 70%.

5. Eficiência energética: consumo de energia 30% menor graças à frenagem regenerativa.

Principais aplicações

1. Embalagem Avançada

• CIs 3D: O adelgaçamento de wafers permite o empilhamento vertical de chips de lógica/memória (por exemplo, pilhas HBM), alcançando largura de banda 10 vezes maior e consumo de energia 50% menor em comparação com soluções 2.5D. O equipamento suporta colagem híbrida e integração TSV (Through-Silicon Via), essenciais para processadores de IA/ML que requerem espaçamento de interconexão <10 μm. Por exemplo, wafers de 12 polegadas adelgaçados para 25 μm permitem o empilhamento de mais de 8 camadas, mantendo uma deformação <1,5%, fundamental para sistemas LiDAR automotivos.

• Embalagem Fan-Out: Ao reduzir a espessura do wafer para 30 μm, o comprimento da interconexão é reduzido em 50%, minimizando o atraso do sinal (<0,2 ps/mm) e possibilitando chiplets ultrafinos de 0,4 mm para SoCs móveis. O processo utiliza algoritmos de retificação com compensação de tensão para evitar deformações (controle de TTV >50 μm), garantindo confiabilidade em aplicações de RF de alta frequência.

2. Eletrônica de Potência

• Módulos IGBT: A redução da espessura para 50 μm diminui a resistência térmica para <0,5 °C/W, permitindo que MOSFETs de SiC de 1200 V operem a temperaturas de junção de 200 °C. Nosso equipamento emprega retificação em múltiplos estágios (grossa: grão de 46 μm → fina: grão de 4 μm) para eliminar danos subsuperficiais, atingindo mais de 10.000 ciclos de confiabilidade em ciclagem térmica. Isso é crucial para inversores de veículos elétricos, onde wafers de SiC com 10 μm de espessura melhoram a velocidade de comutação em 30%.

• Dispositivos de potência GaN-on-SiC: O afinamento do wafer para 80 μm aumenta a mobilidade dos elétrons (μ > 2000 cm²/V·s) para HEMTs GaN de 650 V, reduzindo as perdas de condução em 18%. O processo utiliza corte assistido por laser para evitar rachaduras durante o afinamento, alcançando cortes de borda <5 μm para amplificadores de potência de RF.

3. Optoeletrônica

• LEDs GaN-on-SiC: substratos de safira de 50 μm melhoram a eficiência de extração de luz (LEE) para 85% (em comparação com 65% para wafers de 150 μm) ao minimizar o aprisionamento de fótons. O controle de TTV ultrabaixo do nosso equipamento (<0,3 μm) garante emissão uniforme de LED em wafers de 12 polegadas, o que é crucial para displays Micro-LED que exigem uniformidade de comprimento de onda <100 nm.

• Fotônica de silício: wafers de silício com 25 μm de espessura permitem uma redução de 3 dB/cm na perda de propagação em guias de onda, essencial para transceptores ópticos de 1,6 Tbps. O processo integra o polimento químico-mecânico (CMP) para reduzir a rugosidade da superfície para Ra < 0,1 nm, aumentando a eficiência de acoplamento em 40%.

4. Sensores MEMS

• Acelerômetros: wafers de silício de 25 μm atingem uma relação sinal-ruído (SNR) superior a 85 dB (em comparação com 75 dB para wafers de 50 μm) ao aumentar a sensibilidade ao deslocamento da massa de prova. Nosso sistema de retificação de eixo duplo compensa os gradientes de tensão, garantindo uma deriva de sensibilidade inferior a 0,5% em uma faixa de temperatura de -40 °C a 125 °C. As aplicações incluem detecção de colisões automotivas e rastreamento de movimento em realidade aumentada/virtual.

• Sensores de pressão: A redução da espessura para 40 μm permite faixas de medição de 0 a 300 bar com histerese FS <0,1%. Utilizando colagem temporária (suportes de vidro), o processo evita a fratura do wafer durante a gravação da face posterior, atingindo uma tolerância à sobrepressão <1 μm para sensores industriais de IoT.

• Sinergia Técnica: Nossos equipamentos de adelgaçamento de wafers unificam retificação mecânica, CMP e gravação a plasma para atender a diversos desafios de materiais (Si, SiC, Safira). Por exemplo, o GaN-on-SiC requer retificação híbrida (rebolos de diamante + plasma) para equilibrar dureza e expansão térmica, enquanto sensores MEMS exigem rugosidade superficial inferior a 5 nm por meio de polimento CMP.

• Impacto na Indústria: Ao possibilitar wafers mais finos e de maior desempenho, essa tecnologia impulsiona inovações em chips de IA, módulos 5G mmWave e eletrônicos flexíveis, com tolerâncias TTV <0,1 μm para telas dobráveis e <0,5 μm para sensores LiDAR automotivos.

Serviços da XKH

1. Soluções Personalizadas

Configurações escaláveis: projetos de câmaras de 4 a 12 polegadas com carregamento/descarregamento automatizado.

Suporte para dopagem: receitas personalizadas para cristais dopados com Er/Yb e wafers de InP/GaAs.

2. Suporte de ponta a ponta

Desenvolvimento de processos: Testes gratuitos com otimização.

Treinamento global: Workshops técnicos anuais sobre manutenção e resolução de problemas.

3. Processamento de múltiplos materiais

SiC: Redução da espessura do wafer para 100 μm com Ra <0,1 nm.

Safira: espessura de 50 μm para janelas de laser UV (transmitância >92% a 200 nm).

4. Serviços de Valor Agregado

Fornecimento de consumíveis: Rodas diamantadas (mais de 2000 wafers/vida útil) e pastas de polimento químico-mecânico (CMP).

Conclusão

Este equipamento de adelgaçamento de wafers oferece precisão líder do setor, versatilidade multimaterial e automação inteligente, tornando-o indispensável para integração 3D e eletrônica de potência. Os serviços abrangentes da XKH — da personalização ao pós-processamento — garantem que os clientes alcancem eficiência de custos e excelência de desempenho na fabricação de semicondutores.