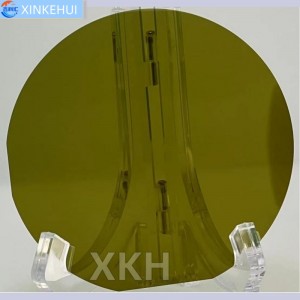

Wafer epitaxial de SiC para dispositivos de potência – 4H-SiC, tipo N, baixa densidade de defeitos

Diagrama detalhado

Introdução

O wafer epitaxial de SiC é fundamental para os modernos dispositivos semicondutores de alto desempenho, especialmente aqueles projetados para operações de alta potência, alta frequência e alta temperatura. A sigla SiC significa Silicon Carbide Epitaxial Wafer (Wafer Epitaxial de Carboneto de Silício) e se refere a uma camada epitaxial de SiC fina e de alta qualidade, cultivada sobre um substrato de SiC maciço. O uso da tecnologia de wafers epitaxiais de SiC está se expandindo rapidamente em veículos elétricos, redes inteligentes, sistemas de energia renovável e aeroespacial devido às suas propriedades físicas e eletrônicas superiores em comparação com os wafers convencionais à base de silício.

Princípios de fabricação de wafers epitaxiais de SiC

A criação de um wafer epitaxial de SiC requer um processo de deposição química de vapor (CVD) altamente controlado. A camada epitaxial é tipicamente cultivada sobre um substrato monocristalino de SiC usando gases como silano (SiH₄), propano (C₃H₈) e hidrogênio (H₂) a temperaturas superiores a 1500 °C. Esse crescimento epitaxial em alta temperatura garante excelente alinhamento cristalino e defeitos mínimos entre a camada epitaxial e o substrato.

O processo inclui várias etapas principais:

-

Preparação do substratoA pastilha de SiC base é limpa e polida até atingir uma suavidade atômica.

-

Crescimento de DCVEm um reator de alta pureza, os gases reagem para depositar uma camada monocristalina de SiC sobre o substrato.

-

Controle de DopingA dopagem do tipo N ou do tipo P é introduzida durante a epitaxia para alcançar as propriedades elétricas desejadas.

-

Inspeção e MetrologiaMicroscopia óptica, AFM e difração de raios X são utilizadas para verificar a espessura da camada, a concentração de dopagem e a densidade de defeitos.

Cada wafer epitaxial de SiC é cuidadosamente monitorado para manter tolerâncias rigorosas em termos de uniformidade de espessura, planicidade da superfície e resistividade. A capacidade de ajustar com precisão esses parâmetros é essencial para MOSFETs de alta tensão, diodos Schottky e outros dispositivos de potência.

Especificação

| Parâmetro | Especificação |

| Categorias | Ciência dos Materiais, Substratos Monocristalinos |

| Politipo | 4H |

| Doping | Tipo N |

| Diâmetro | 101 mm |

| Tolerância de diâmetro | ± 5% |

| Grossura | 0,35 mm |

| Tolerância de espessura | ± 5% |

| Comprimento plano primário | 22 mm (± 10%) |

| TTV (Variação Total da Espessura) | ≤10 µm |

| Urdidura | ≤25 µm |

| FWHM | ≤30 segundos de arco |

| Acabamento da superfície | Rq ≤0,35 nm |

Aplicações de wafers epitaxiais de SiC

Os produtos de wafer epitaxial de SiC são indispensáveis em diversos setores:

-

Veículos Elétricos (VEs)Dispositivos baseados em wafers epitaxiais de SiC aumentam a eficiência do sistema de propulsão e reduzem o peso.

-

Energia renovávelUtilizado em inversores para sistemas de energia solar e eólica.

-

Fontes de alimentação industrialPermite comutação de alta frequência e alta temperatura com menores perdas.

-

Aeroespacial e DefesaIdeal para ambientes agressivos que exigem semicondutores robustos.

-

Estações Base 5GOs componentes de wafer epitaxial de SiC suportam densidades de potência mais elevadas para aplicações de radiofrequência.

O wafer epitaxial de SiC permite designs compactos, comutação mais rápida e maior eficiência de conversão de energia em comparação com os wafers de silício.

Vantagens do wafer epitaxial de SiC

A tecnologia de wafers epitaxiais de SiC oferece benefícios significativos:

-

Alta tensão de rupturaSuporta tensões até 10 vezes maiores que as de wafers de silício.

-

Condutividade térmicaO wafer epitaxial de SiC dissipa o calor mais rapidamente, permitindo que os dispositivos funcionem com temperaturas mais baixas e de forma mais confiável.

-

Altas velocidades de comutaçãoMenores perdas de comutação permitem maior eficiência e miniaturização.

-

Banda largaGarante estabilidade em tensões e temperaturas mais elevadas.

-

Robustez do MaterialO SiC é quimicamente inerte e mecanicamente resistente, ideal para aplicações exigentes.

Essas vantagens fazem do wafer epitaxial de SiC o material de escolha para a próxima geração de semicondutores.

FAQ: Wafer Epitaxial de SiC

P1: Qual a diferença entre um wafer de SiC e um wafer epitaxial de SiC?

Uma pastilha de SiC refere-se ao substrato em massa, enquanto uma pastilha epitaxial de SiC inclui uma camada dopada especialmente cultivada para ser usada na fabricação de dispositivos.

Q2: Quais são as espessuras disponíveis para as camadas de wafer epitaxial de SiC?

As camadas epitaxiais normalmente variam de alguns micrômetros a mais de 100 μm, dependendo dos requisitos da aplicação.

P3: O wafer epitaxial de SiC é adequado para ambientes de alta temperatura?

Sim, o wafer epitaxial de SiC pode operar em condições acima de 600°C, superando significativamente o silício.

Q4: Por que a densidade de defeitos é importante em wafers epitaxiais de SiC?

Uma menor densidade de defeitos melhora o desempenho e o rendimento do dispositivo, especialmente para aplicações de alta tensão.

Q5: Estão disponíveis wafers epitaxiais de SiC do tipo N e do tipo P?

Sim, ambos os tipos são produzidos utilizando um controle preciso do gás dopante durante o processo epitaxial.

Q6: Quais são os tamanhos de wafer padrão para wafers epitaxiais de SiC?

Os diâmetros padrão incluem 2 polegadas, 4 polegadas, 6 polegadas e, cada vez mais, 8 polegadas para fabricação em grande volume.

Q7: Como o wafer epitaxial de SiC impacta o custo e a eficiência?

Embora inicialmente mais caro que o silício, o wafer epitaxial de SiC reduz o tamanho do sistema e a perda de energia, melhorando a eficiência de custos total a longo prazo.